IP_UNI_XILINX

Description

The IP-UNI-Xilinx is a general purpose digital IndustryPack™ module. It is based on the XCS40XL FPGA of the SpartanXL™-family from XILINX. The use of a FPGA gives to the user full flexibility to implement a design according to the needs. The configuration of the FPGA is loaded from a serial PROM. On one side the FPGA is directly connected to the IP-Interface connector and on the other side it has connections via buffers to the I/O-connector. The module provides up to 24 bi-directional I/O lines which are able to drive a load of 25Ohm. These lines can be configured in groups of 8 either as input or output or as bidirectional data lines. In addition it has 2 TTL-compatible input lines and one TTL-compatible output line. An input line to a comparator offers the possibility to connect a signal other then TTL. It must be in the range of 0 to 5V. No threshold setting is necessary because it is selfadjusted to the mean value of the incoming signal. Two digital 5-tap delay lines driven by the FPGA allow to feedback data. The FPGA can be clocked either by the internal 9MHz crystal oscillator or by an external clock signal connected via the I/O-connector of the modul. This option is selectable by a jumper. A 8-bit header is connected to the FPGA. It can be used to monitor some test signals or as a field of jumpers for selectable user options (for instance in decoder applications).

Specification

- 24 I/O’s with 25Ohm Driver capability (in groups of 8 configurable either as input, output or bi-directional I/O)

- 1 comparator input with selftracking threshold

- 2 TTL-compatible logic inputs (50Ohm-terminated)

- 1 TTL-compatible clock input for external device clock (50Ohm-terminated)

1 TTL-compatible output (Iout_low = 24mA)

- XILINX-FPGA XCS40XL containing the IP-Interface and user specified logic, configurable via a serial configuration PROM

- 2 On-board 5-tap delay lines (5 x 20ns)

- 9MHz crystal oscillator

- 8-bit header for use in decoder functions or to select other user specified options implemented in the FPGA design

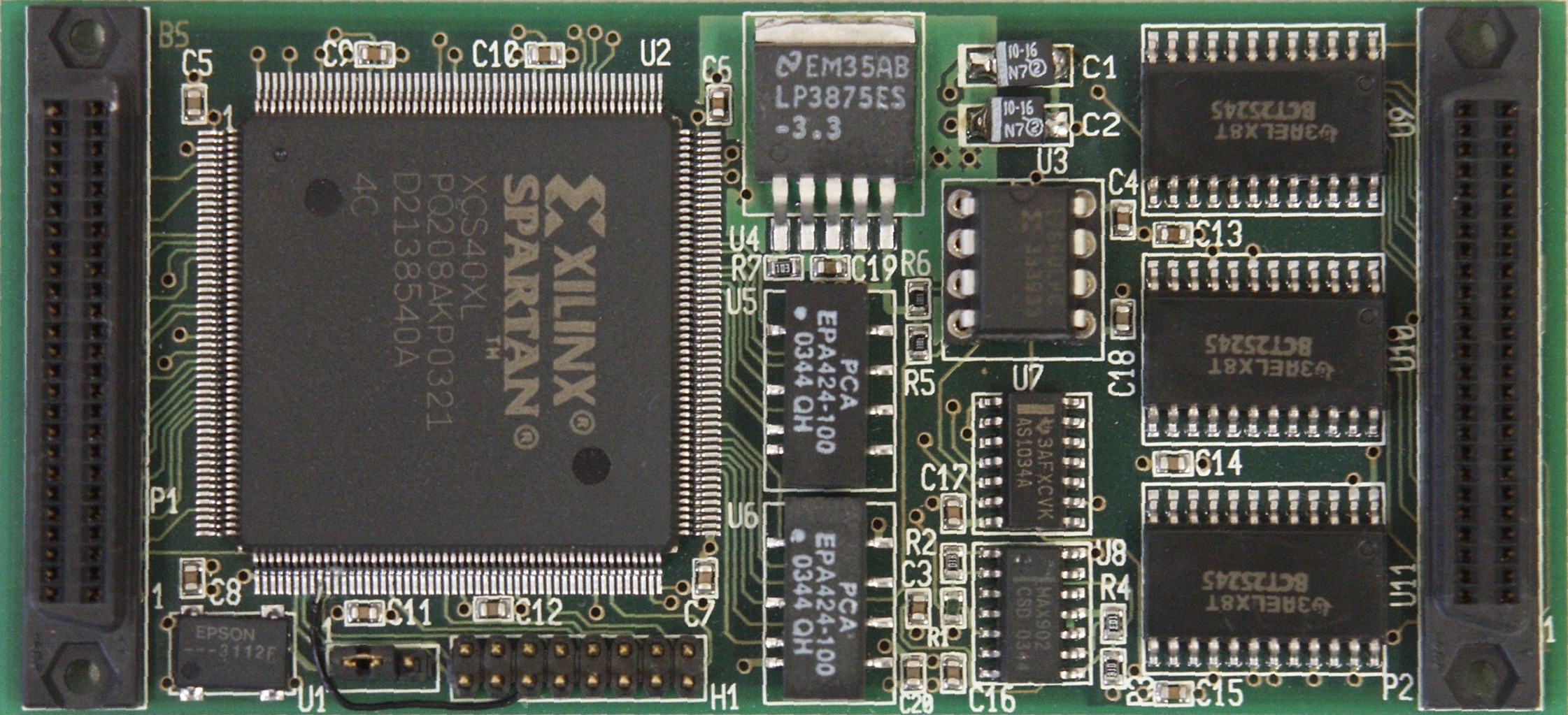

Board Photograph

Documentation

A more detailed description of the module can be found here. Caution: There are two board revisions available. In the second revision a minor error in the design was corrected. The consequence of that change is that one has always to use different configuration PROMs for the given application realizing the same logic but using different pins of the FPGA. You can distinguish the revisions by the serial number. The serial numbers for revision on are from 1-40. The newer boards start with serial number 100.